# Revolution EDA

MURAT ESKIYERLI, PhD

EMAIL: ESKIYERLI@REVEDA.EU

TEL: +31 6 4200 7540

WEBSITE: WWW.REVEDA.EU

# Why A Revolution?

- Electronic-design automation is the enabling technology of semiconductor industry.

- Closest analogy is the Software IDEs.

- MS Visual Studio vs Visual Studio Code.

- Latter's power is in its extendibility.

- Model Revolution EDA is pursuing.

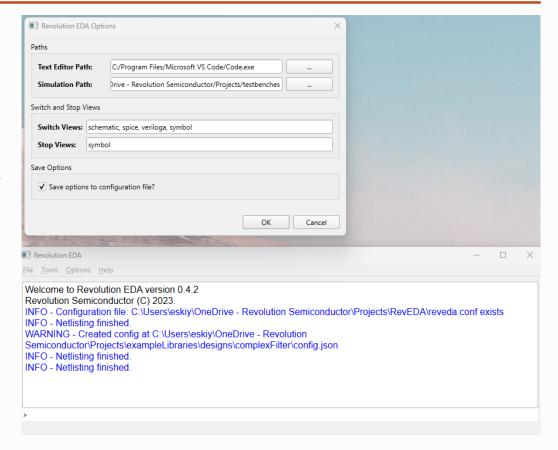

#### RevEDA Main Window

- Includes a full a Python interpreter.

- Access to configuration options and tools such as Verilog-A module import.

- It also highlights errors and warnings.

- o reveda.log file has the same info.

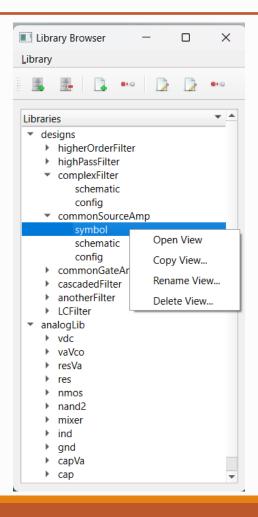

# Library Browser

- Library Browser should be familiar to most

IC designers.

- Library, cell and cell view creation, editing, renaming and deletion done at Library

Browser.

- Library paths are also defined in the library path editor.

# Design Entry

- Revolution EDA has robust design entry tools:

- All-around Python based.

- Built-in Python console.

- State-of-the-art QT6 toolkit.

- What is Next?

- Layout Editor

- Simulation GUI cockpit.

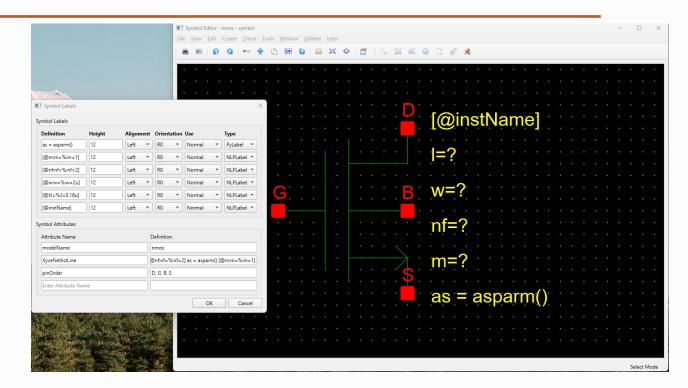

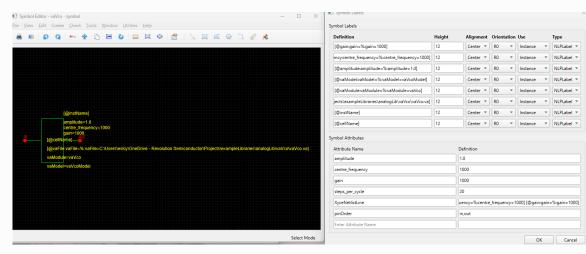

## Symbol Editor

- RevEDA Symbol Editor can capture:

- Properties common to all instances (attributes)

- Properties that can change per instance (labels)

- Python Labels (*PyLabel*) allow full use

Python functions for instance callbacks.

No more messing with Tcl or SKILL.

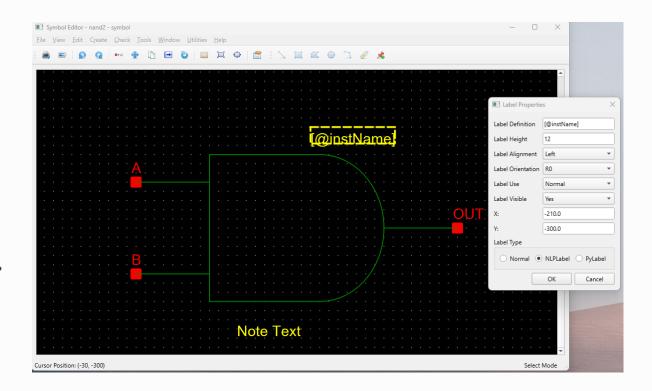

# Symbol Editor

- Lines, Circles, Rectangles and arches can be drawn.

- Pins and labels can be added.

- Labels can be visible or hidden.

- Normal labels can be used at notes on symbol.

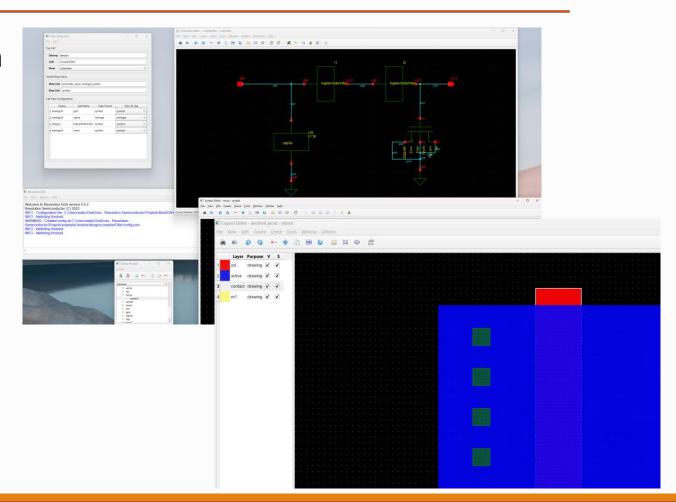

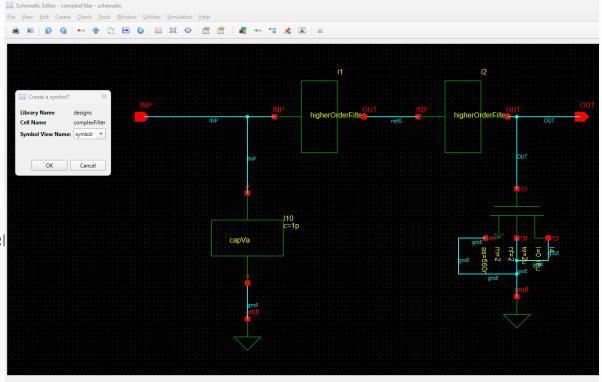

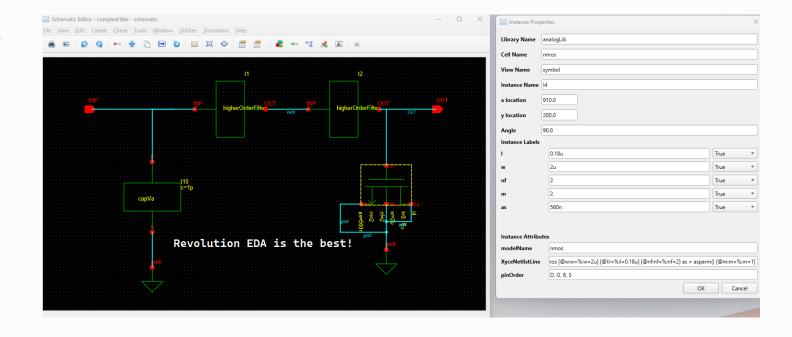

#### Schematic Editor

- Schematic Editor

- Hierarchical, a symbol can be generated for each schematic.

- Some instance labels are automatically generated.

- Other instance labels can be entered per instance based (NLPLabels)

- PyLabels generated using associated callback functions.

### Schematic Editor

- Net editing is constantly improving:

- Net naming

- Net merging

- Snapping to instance pins

- Snapping to other net end points.

- Global nets defined using symbols (gnd, vdd, etc).

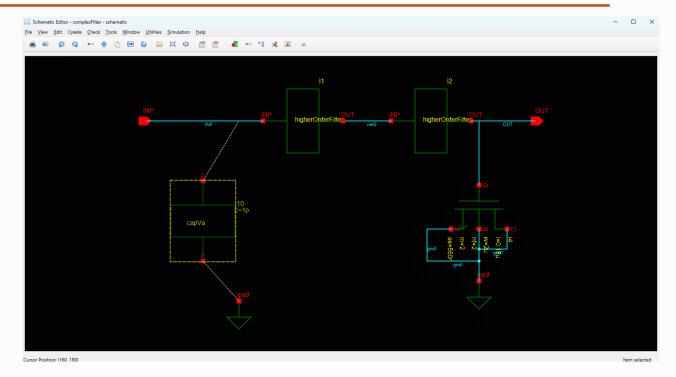

### Schematic Editor

- Instance properties (labels),

location, and angle can be

changed using dialogues.

- Schematic cells can be traversed both up and down.

- Text notes can be added to schematics.

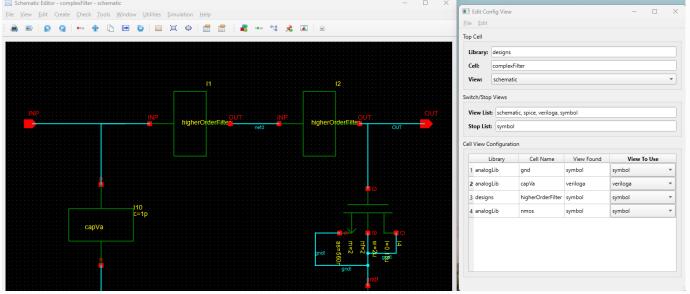

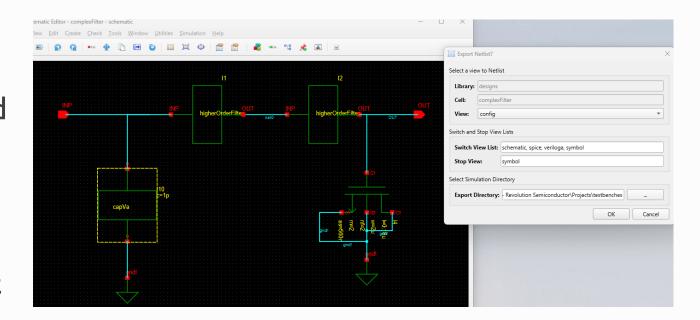

# Config Editor

RevEDA config editor allows

per cell based steering of circuit netlisting.

- Familiar interface for experienced users.

- Displayed cells adapt to selected cellview.

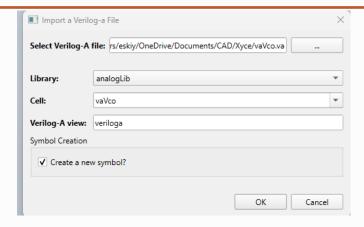

# Verilog-A module Import

- Verilog-A module import is experimental and currently only for Xyce simulator.

- A symbol can be generated for any module.

- Including labels and attributes for model and instance parameters.

- ongspice support is planned.

# Netlisting

- Hierarchical netlisting is possible:

- Switch view list based

- Config view based

- PyLabel values will be carried to netlist.

- Full power of Python for all modelling needs.

```

** Revolution EDA CDL Netlist

** Library: designs

** Top Cell Name: complexFilter

** View Name: schematic

** Date: 2023-05-22 11:39:34.931902

*.GLOBAL gnd!

XI1 higherOrderFilter INP net0

.SUBCKT higherOrderFilter INP OUT

MI10 gnd! OUT gnd! gnd! nmos w=2u l=0.18u nf=2 as=560n m=2

Ycapacitor I9 INP gnd! capacitorModel c=1p

XI6 highPassFilter gnd! OUT INP

.SUBCKT highPassFilter VSS OUT INP

RI2 INP OUT R=1k

CI4 OUT VSS C=1p

. ENDS

. ENDS

XI2 higherOrderFilter net0 OUT

Ycapacitor I10 INP gnd! capacitorModel c=1p

MI4 gnd! OUT gnd! gnd! nmos w=2u l=0.18u nf=2 as=560n m=2

. END

```

# Netlisting

- Still being worked on.

- Hierarchical netlisting steered by switch view list setting or config view.

- Currently targeting Xyce, but ngspice support is planned.

# PDK Support

- PDK location can be defined using REVEDASIM\_PATH environment variable or using .env file.

- o PDK directory should be named pdk and instance callbacks should be defined in callbacks.py file.

- Each cell will have a separate class defined.

- Python label values can depend on other label values.

```

class baseInst():

def init (self, labels dict: dict):

self. labelsDict = labels dict

class res(baseInst):

def init (self, labels dict:dict):

super(). init (labels dict)

def doubleR(self):

Rvalue = self._labelsDict.get('R').labelValue

if Rvalue.isalnum():

return str(2*Quantity(Rvalue))

return '?'

class nmos(baseInst):

def _ init (self, labels dict:dict):

super().__init__(labels_dict)

self.w = Quantity(self. labelsDict['w'].labelValue)

self.l = Quantity(self._labelsDict['l'].labelValue)

self.nf= Quantity(self._labelsDict['nf'].labelValue)

self.sd1p8v = 0.28

self.sa1p8v = sb1p8v = 0.265

self.sourceDiffs = lambda nf: int(int(nf) / 2 + 1)

def asparm(self):

return self.sourceDiffs(self.nf)*(self.w/self.nf)*self.sd1p8v

```

15

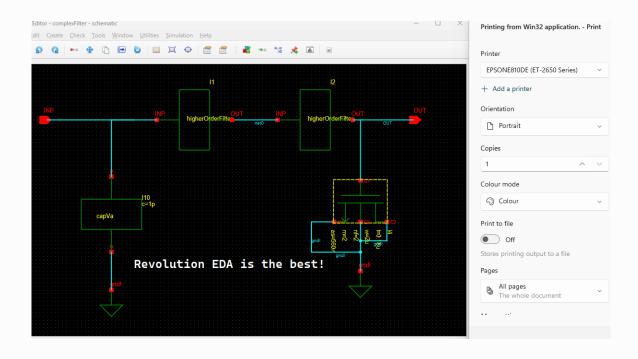

# Print and Image Export Support

- Schematics and symbols

can be printed using system

printers.

- Schematics and symbol

drawings can be exported to

common graphics formats.

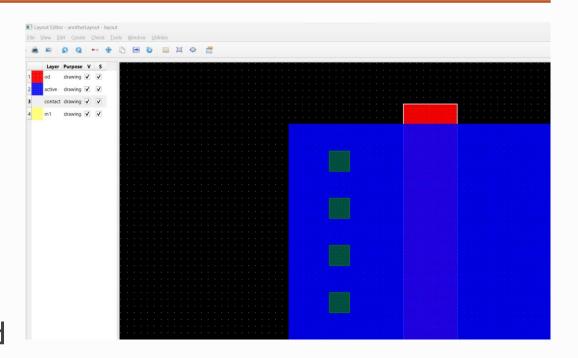

# Layout Editor

- Layout Editor is the new focus.

- Python-based parametric cells.

- Gdstk library is used for GDS export.

- Schematic-driven-Layout flow would be possible when integrated with Schematic Editor.

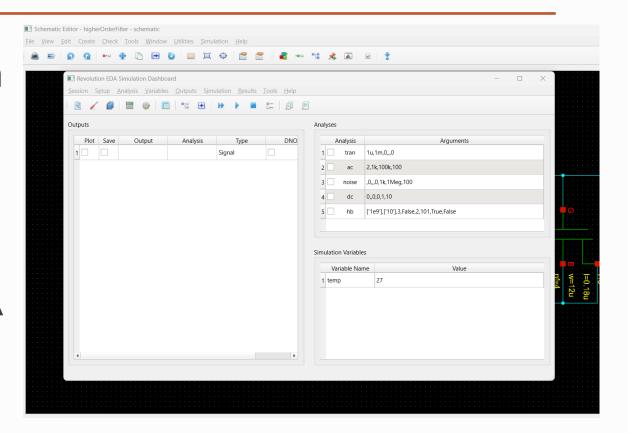

## Simulation GUI

A fully-fledged simulation

GUI targeting Xyce based

on Glade was done.

Porting to Revolution EDA has started.

#### What does RevEDA need?

- A full-fledged PDK

- Symbols

- Instance callbacks

- Parametric cells

- Device Models

- Testing, testing and more testing.

- Software unit tests.

- User tests.

- Test tape-outs.

# One last thing...

It is buggy, but who isn't?

```

elp.log file.

Cadence Help logging started at /′ :/users/ /.config/cadence/cdnshelp.log file.

virtuoso: YieldData.cpp:1596: void pointStrategy::YieldData::TotalYield::addPoint(const std::map<int, boost::option

al<double> >&, const std::map<int, std::pair<double, double> >&, std::string, const std::map<std::basic_string<char

>, std::set<std::basic_string<char> > >&, const std::map<int, int>&): Assertion `measVals.size()<=size_t(numSpecs()

)' failed.

```

Any ideas for future development, add-ons, etc.?