for high

performance

microelectronics

# OpenPDK SG13G2 – Current Status, Roadmap and Open Questions

Sergei Andreev – Scientist Technology / Research & Prototyping Service

Networking Workshop FMD-QNC 'OpenPDK, OpenTooling and Open Source Design – An Initiative to Push Development'

June 27/28 2023

- 1. IHP Open Source EDA Flows Proposals

- 2. OpenPDK Project on GitHub

- 3. Dedicated OpenPDK Virtual Linux Host Machine

- 4. Available OpenPDK Data

- 5. Open Questions

- 6. Next Steps / Planned Updates

- 7. Summary / Goals

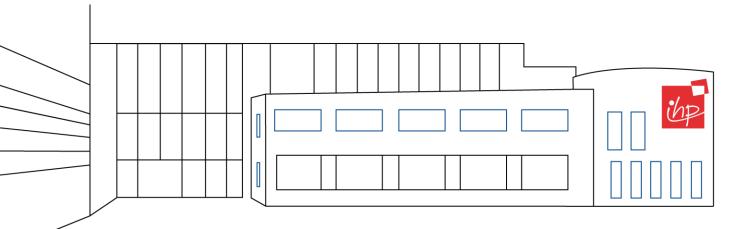

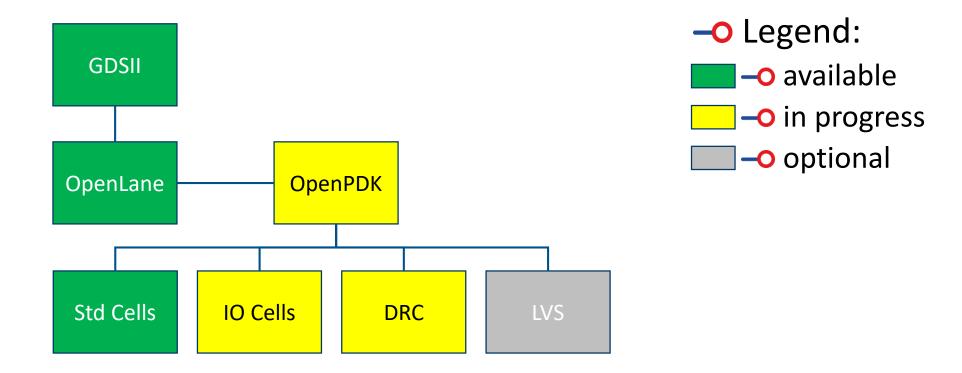

# Digital Open Source Development Flow

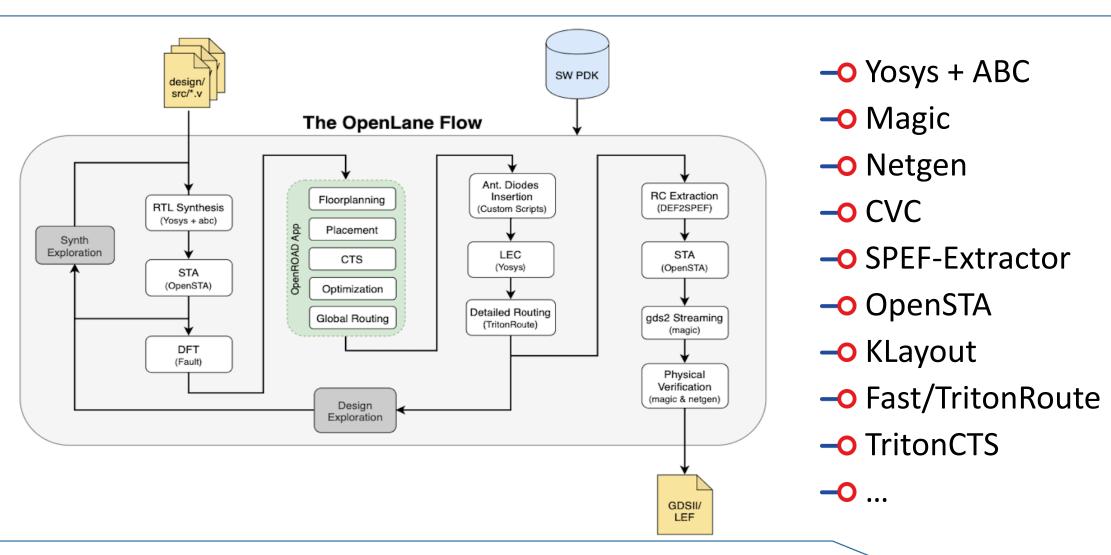

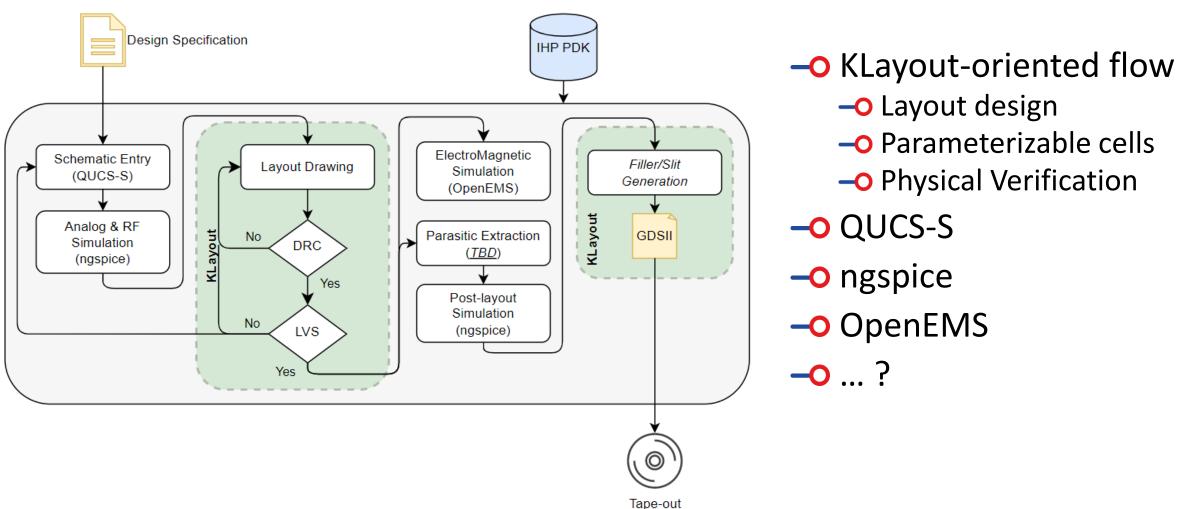

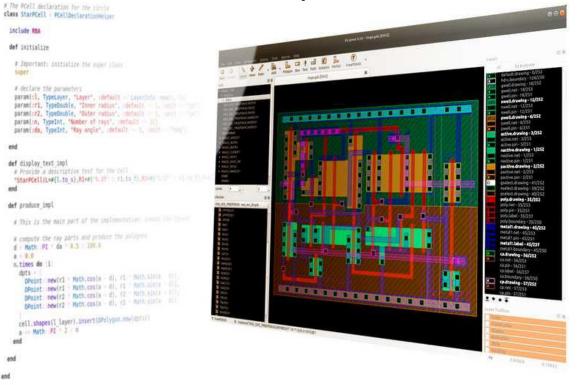

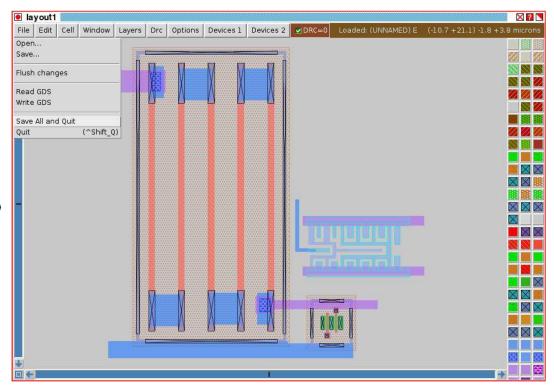

# Analog/RF OpenPDK/EDA Flow Proposal

- 1. | IHP Open Source EDA Flows Proposals

- 2. OpenPDK Project on GitHub

- 3. Dedicated OpenPDK Virtual Linux Host Machine

- 4. Available OpenPDK Data

- 5. Open Questions

- 6. Next Steps / Planned Updates

- 7. Summary / Goals

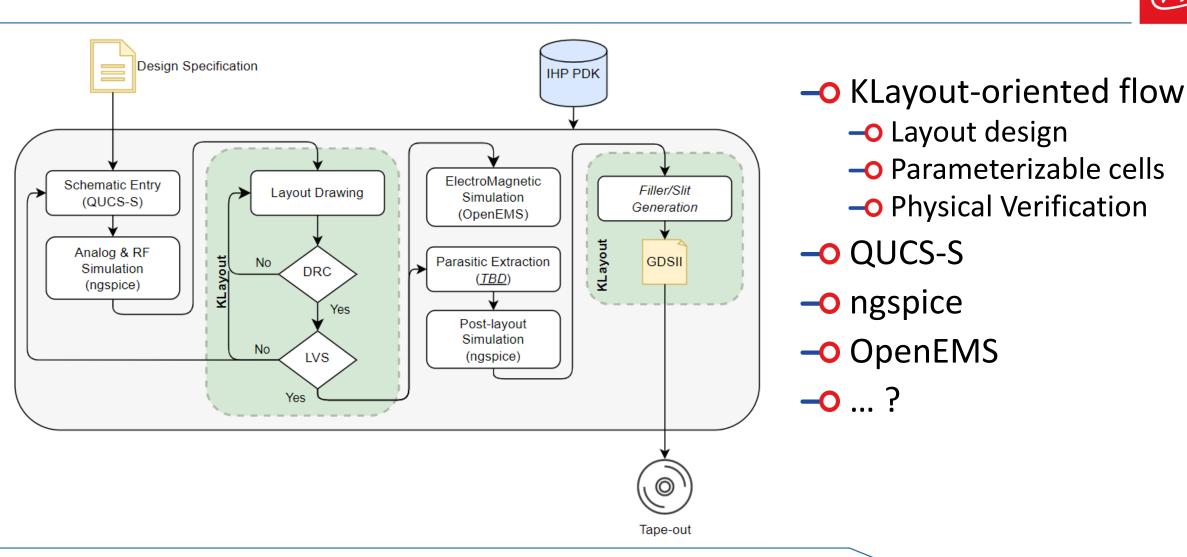

# OpenPDK Project on GitHub

#### **PDK Contents:**

- Base cell set with limited set of standard logic cells (Open130-G2)

- GDSII view of primitive devices

- KLayout layer property and tech files

- SPICE Models of HBT devices

- OpenEMS: tutorials, scripts, documentation

- SG13G2 Process specification

- → SG13G2 Layout Rules

- MOS/HBT Measurements in MDM format

- Project Roadmap Gantt chart

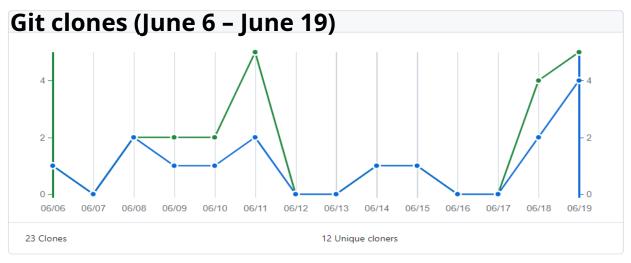

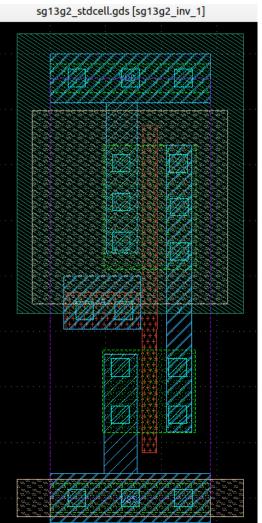

# OpenPDK GitHub Project Traffic (last two weeks)

| Referring sites        |       |                 |

|------------------------|-------|-----------------|

| Site                   | Views | Unique visitors |

| ⊕ Google               | 507   | 45              |

| ⊕ github.com           | 222   | 8               |

| ⊕ t.co                 | 67    | 8               |

| mgspice.sourceforge.io | 25    | 3               |

| ⊕ linkedin.com         | 20    | 1               |

| ⊕ DuckDuckGo           | 8     | 4               |

| infineon.webex.com     | 6     | 1               |

| ⊕ cn.bing.com          | 6     | 1               |

| → yandex.ru            | 1     | 1               |

| ecosia.org             | 1     | 1               |

- 1. | IHP Open Source EDA Flows Proposals

- 2. OpenPDK Project on GitHub

- 3. Dedicated OpenPDK Virtual Linux Host Machine

- 4. Available OpenPDK Data

- 5. Open Questions

- 6. Next Steps / Planned Updates

- 7. Summary / Goals

# Dedicated OpenPDK Virtual Linux Host Machine

- Virtual Machine (VMWare VSphere) with Linux OS

- **→** 4 CPU

- → Memory 16GB

- -0 HD 1TB

- OS Ubuntu 22.04.2 LTS

- → SSH, FTP, ThinLinc servers

- Only internal users by request

- Automatic backup every 24h at night

| PDK           | sky130 [GitHub, open_pdks]                                                               |

|---------------|------------------------------------------------------------------------------------------|

| Layout        | KLayout [Deb package, v0.28] Magic [GitHub] KiCAD [6.0.2] gdspy [1.6.12] netgen [GitHub] |

| Schematic     | Xschem [GitHub] QUCS-S [GitHub] Revolution EDA [GitHub]                                  |

| Simulation    | Ngspice [GitHub]  Xyce [GitHub]  spectre2spice [GitHub]                                  |

| Modeling      | DMT [GitHub, user-level] OpenVAF [23.2.0]                                                |

| EM            | OpenEMS [GitHub] Octave [6.4.0]                                                          |

| Flows         | Open_pdks [GitHub, user-level] OpenLane [GitHub, user-level]                             |

| PCells        | OpenPCells [GitHub, user-level] Magic TCL & KLayout Python Pcells [GitHub, sky130]       |

| Gen           | PDKMaster [0.9.0, PyPi]                                                                  |

| Documentation | doxygen [1.9.1]<br>graphviz [2.43.0]                                                     |

- 1. | IHP Open Source EDA Flows Proposals

- 2. OpenPDK Project on GitHub

- 3. Dedicated OpenPDK Virtual Linux Host Machine

- 4. Available OpenPDK Data

- 5. Open Questions

- 6. Next Steps / Planned Updates

- 7. Summary / Goals

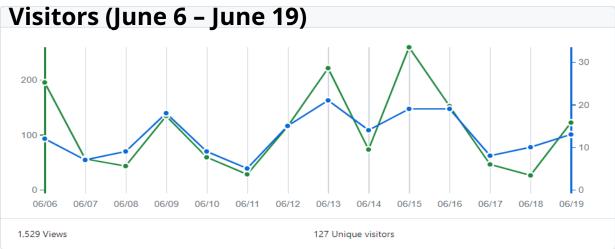

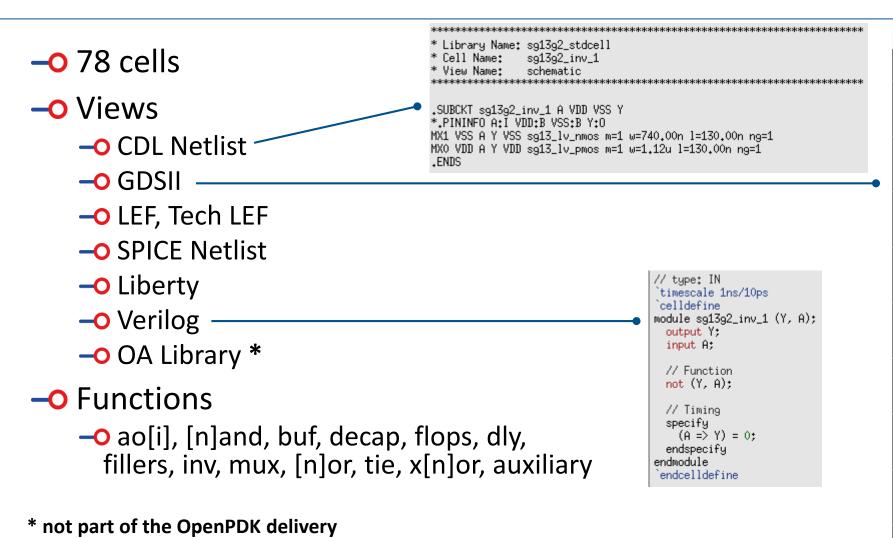

# Base Cell Set with Digital Standard Cells

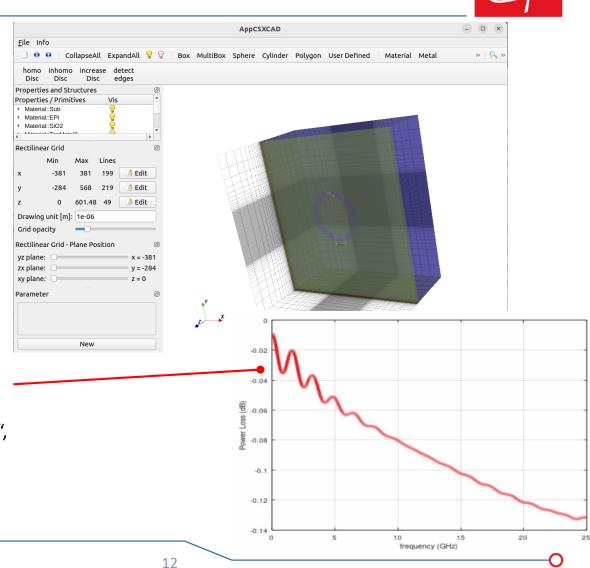

# OpenEMS ElectroMagnetic Solver Review

- **─** 3D FDTD solution targeting RF EM simulations

- Model built by Python or Octave/Matlab scripting

- Graphical viewer for model + mesh (CSXCAD)

- → Some interfaces to EDA packages, but no KLayout support yet

- No internal support for GDSII import, interface was created using Python library gdspy

- Variable FDTD grid spacing, mesh smoothing

- Semiconductor substrate support (permittivity + conductivity)

- S-Parameter output

- Useful tutorials for RF examples

- Possible issue: small residual energy at low frequency or DC might create DC leakage in simulation results

- Efficient solution in commercial FDTD tools is "resonance estimation", but that is not implemented in OpenEMS so far

- O Mostly manual mesh definition

- -o automatic meshing add-on project (OpenMesh) unfinished

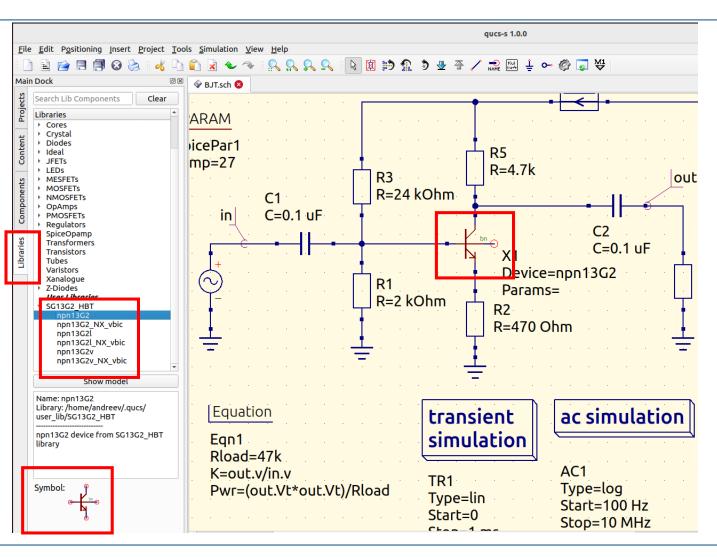

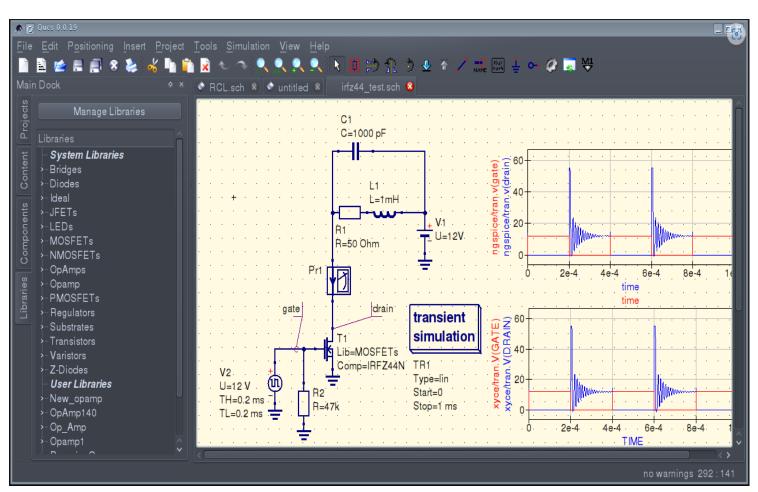

# QUCS-S Custom Library with IHP OpenPDK Devices

```

<Symbol>

<Line -30 0 10 0 #000080 2 1>

<Line -20 0 10 0 #800000 2 1>

<Line 0 -15 0 -5 #800000 2 1>

<Line -10 -5 10 -10 #800000 2 1>

<Line 0 -20 0 -10 #800000 2 1>

<Line 0 -20 0 -10 #800000 2 1>

<Line -10 5 10 10 #800000 2 1>

<Line -6 15 6 0 #800000 2 1>

<Line 0 9 0 11 #800000 2 1>

<Line 0 9 0 10 #000080 2 1>

<Line 0 10 0 0 #800000 2 1>

<Line -10 0 20 0 #800000 2 1>

<Line -10 -15 0 30 #800000 3 1>

<Text 5 -10 5 #005500 0 "bn">

<.PortSym 0 -30 1 90>

<.PortSym 0 -30 1 90>

<.PortSym 0 30 3 270>

<.PortSym 20 0 4 180>

<.ID 10 10 X>

</Symbol>

```

Directory structure of user lib:

```

~/.qucs/

— user_lib

|— SG13G2_HBT

| SG13G2_HBT.sym

— SG13G2_HBT.lib*

```

<sup>\*</sup> HSPICE models file from OpenPDK without any modifications

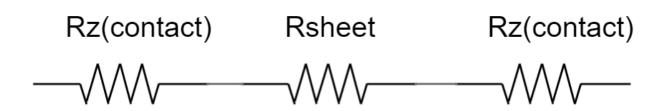

## **Resistor Models**

- Spice Models Ready for

- Rsil (Rs= 7  $\Omega/\Box$ )

- $\multimap$  Rhigh (Rs= 1360 Ω/□)

- $\rightarrow$  Rppd (Rs= 260  $\Omega/\Box$ )

- Temperature Modeling

- Noise Modeling

- Ngspice, Xyce compatible

- Non-linear effects not included:

- Self heating

- Velocity saturation

- **→** ...

- Working on adapting R3 CMC resistor model.

Simple linear spice semiconductor resistor model

- 1. IHP Open Source EDA Flows Proposals

- 2. OpenPDK Project on GitHub

- 3. Dedicated OpenPDK Virtual Linux Host Machine

- 4. Available OpenPDK Data

- 5. Open Questions

- 6. Next Steps / Planned Updates

- 7. Summary / Goals

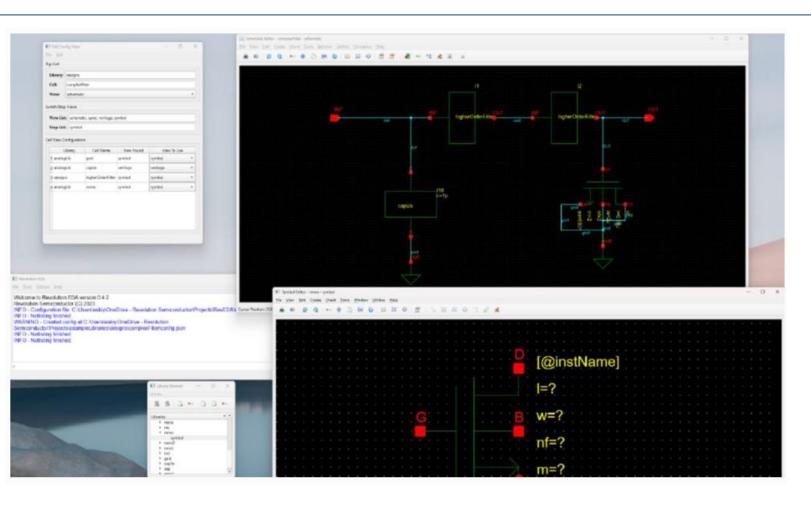

# Analog/RF OpenPDK/EDA Flow Proposal

# Layout Design: should we support Magic VLSI?

#### KLayout

# Magic

# Circuit Design: QUCS-S / Xschem / Revolution EDA

- Direct support of SPICE models from components datasheets

- Basic and Advanced SPICE components and simulations

- Direct support of SPICE Modelcards, SPICE sections (.IC, .NODESET)

- Parametric circuits (.PARAM) and SPICE postprocessor (Nutmeg)

- Single-tone and Multitone Harmonic balance analysis w/ XYCE backend

- Nutmeg script simulation

- XYCE script simulation type and digital device library

- XSPICE CodeModel synthesizer

- User mathematical functions definitions with .FUNC (added in 0.0.20)

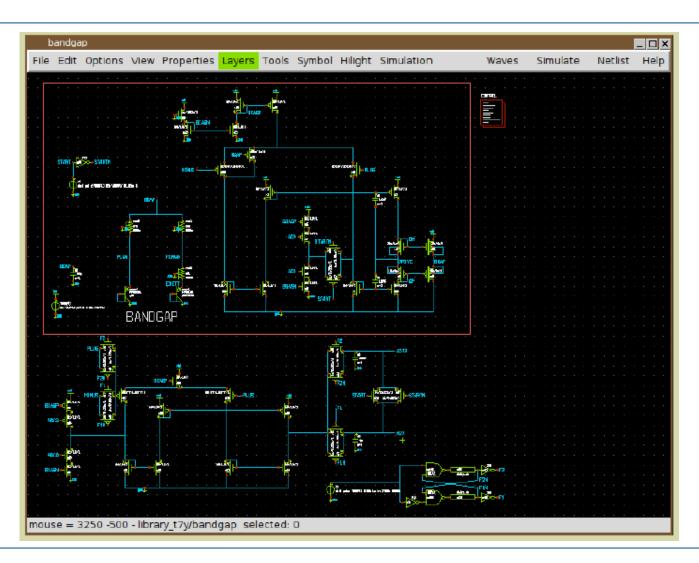

# Circuit Design: QUCS-S / Xschem(?) / Revolution EDA

- Hierarchical representation of circuits

- Generate circuit netlists for SPICE, Verilog, VHDL, tEDAx

- Components: primitives, behavioral blocks, subcircuit blocks

- True mixed mode circuit description: Analog, Behavioral, Transistor-level, Gate-level

- Efficient handling of Very large designs, no scripting language for intensive computations

- → GUI and scripting language with Tcl-Tk

- Vector instances and bus notations like DATA[15:0,31:16]

- TCL API for forward / backward annotation to / from 3rd party EDA software

- Used for SkyWater OpenPDK

# Circuit Design: QUCS-S / Xschem / Revolution EDA(?)

- Revolution EDA has robust symbol and schematic entry tools

- → All-around Python based.

- → Built-in Python console.

- State-of-the-art QT6 toolkit.

- Shared-source (MPL modified with Commons Clause)

- **→** Big ambitions:

- Layout Editor

- Simulation GUI cockpit

- Al in circuit design, and much more...

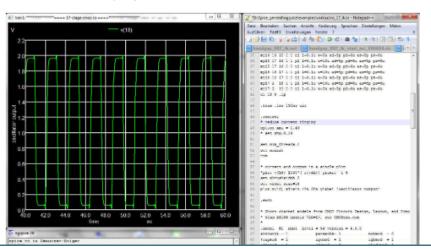

# Simulation: should we support Xyce?

# Home What is ngspice ? Features, Extras & Options F.A.Q. Tutorials Introductory and update videos Sourceforge Developer

#### ngspice - open source spice simulator

ngspice is the open source spice simulator for electric and electronic circuits.

Such a circuit may comprise of JFETs, bipolar and MOS transistors, passive elements like R, L, or C, diodes, transmission lines and other devices, all interconnected in a netlist. Digital circuits are simulated as well, event driven and fast, from single gates to complex circuits. And you may enter the combination of both analog and digital as a mixed-signal circuit.

ngspice offers a wealth of device models for active, passive, analog, and digital elements. Model parameters are provided by our <u>collections</u>, by the <u>semiconductor device manufacturers</u>, or from <u>semiconductor foundries</u>. The user adds her circuits as a netlist, and the output is one or more graphs of currents, voltages and other electrical quantities or is saved in a data file.

ngspice does not provide schematic entry. Its input is command line or file based. There are however third party interfaces available.

#### **About Xyce**

Xyce is an open source, SPICE-compatible, high-performance analog circuit simulator, capable of solving extremely large circuit problems by supporting large-scale parallel computing platforms. It also supports serial execution on all common desktop platfori small-scale parallel runs on Unix-like systems. In addition to analog electronic simula: Xyce has also been used to investigate more general network systems, such as neural networks and power grids. Read more about Xyce.

- 1. | IHP Open Source EDA Flows Proposals

- 2. OpenPDK Project on GitHub

- 3. Dedicated OpenPDK Virtual Linux Host Machine

- 4. Available OpenPDK Data

- 5. Open Questions

- 6. Next Steps / Planned Updates

- 7. Summary / Goals

# Next Steps / Planned Updates

- Start set of Digital cells

- Additional cells in development by ETH Zurich + community

- LEF view for primitive devices

- KLayout Technology file

- Add connectivity section

- **⊸** Need help on:

- MOS SPICE models

- PCells

#### **→** Tasks on GitHub:

|    | Title                                                  | Status      | ••• |

|----|--------------------------------------------------------|-------------|-----|

| 1  | O Ngspice: 'ignored parameter' messages for HBT models | Done        | -   |

| 2  | C Start set of Digital cells                           | Done        | -   |

| 3  | Digital standard cells enhancements (increased set)    | In Progress | -   |

| 4  | C LEF view for primitive devices                       | Todo        | ~   |

| 5  | ( ) MOS HSPICE models                                  | Todo        | -   |

| 6  | ( ) KLayout Tech file                                  | Done        | ~   |

| 7  | O DRM for Opensource PDK                               | Done        | -   |

| 8  | O QUCS-S Library w/ IHP OpenPDK devices                | In Progress | -   |

| 9  | Move documentation to ReadTheDocs framework            | Todo        | -   |

| 10 | () PyCells                                             | Todo        | ,   |

|    |                                                        |             |     |

## **MOS SPICE Models**

- SG13G2 MOS Spectre models to SPICE format conversion to use with ngspice/Xyce simulators

- **→** supported:

- extreme value behavior, corner cases

- transistor layout data transfer

- drain/source area calculations using the fingers number

- some Spectre commands/instructions/statements not supported:

- geometry checks

- static and dynamic states checks

- -o statistical variations

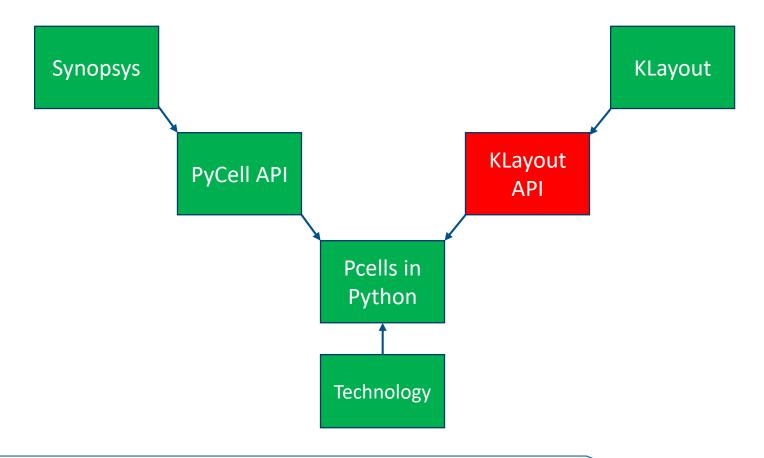

# **OpenPDK Pcells**

SG13G2 Synopsys PyCells to KLayout Python Pcells conversion

- 1. | IHP Open Source EDA Flows Proposals

- 2. OpenPDK Project on GitHub

- 3. Dedicated OpenPDK Virtual Linux Host Machine

- 4. Available OpenPDK Data

- 5. Open Questions

- 6. Next Steps / Planned Updates

- 7. Summary / Goals

# Summary / Goals

→ First phase goal → Digital design submitted w/ core expert group in Dec Y23

# Acknowledgment

- Thanks to my colleagues at IHP

- Thanks to ETH Zurich + open source community

- Separate thanks to Volker Mühlhaus for work on the EM solvers

- And final thanks to different public founded German projects:

- → VE-HEP (16KIS1339K) https://elektronikforschung.de/projekte/ve-hep-1

- -O IHP Open130-G2 (16ME0852) https://www.elektronikforschung.de/projekte/ihp-open130-g2

- FMD-QNC (16ME0831) https://www.elektronikforschung.de/projekte/fmd-qnc

- Workshop funding FMD-QNC with VDI/VDE (project management agency) approval

SPONSORED BY THE

# Thank you for your attention!

**IHP – Leibniz Institute for High Performance Microelectronics**

Im Technologiepark 25

15236 Frankfurt (Oder)

Tel.: +49 (0) 335 5625 733

E-Mail: andreev@ihp-microelectronics.com